Invalidation Search Sample in Chinese Language

From DolceraWiki

互补型逻辑输入并联(CLIP)场效应晶体管(FET)逻辑电路

现有技术中的技术问题和解决方案

技术问题

- 在传统CMOS逻辑门电路中负载晶体管的串联降低了栅极的切换率和开关速度,同时也减少了栅极上的输入端数量(也叫“扇入”)。

解决方案

- 为了克服上述问题,因而提出了全并联的CMOS栅极设计。其中,用第一负载取代串联负载晶体管,第一负载可以是一个MOS晶体管或者电阻;第二负载包含一个与驱动晶体管具有相反导电性的MOS晶体管。

- 公开了一种高速,高密度,低功耗的互补型FET逻辑电路,其中,逻辑门的互补型FET反相器输出状态的的电压传输函数故意地偏移,从而大大降低逻辑门的延迟间隔,因此也显著增加了栅极的速度。

本发明的技术问题和解决方案(CLIP 和/或逻辑电路)

根据本发明的CLIP 和/或逻辑电路

技术问题一

- 上升和延迟时间增加

解决方案

- 对于高速逻辑电路,栅极的上升和延迟时间最小化。换句话说,栅极提供一个精确反映逻辑输入信号状态的逻辑输出信号,该栅极的内部延迟一定是最小化的。

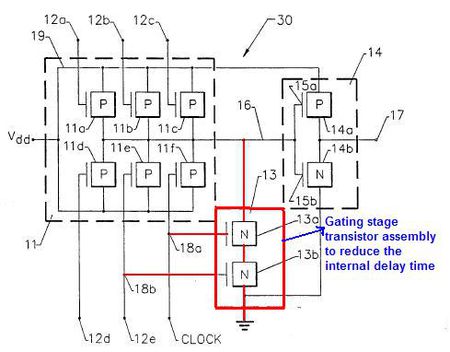

- 根据本发明,当开关FET采用如上所述的空间排布时,发现逻辑门的内部延迟大大降低,从而在保证逻辑开关可靠性的同时提高了栅极的速度。

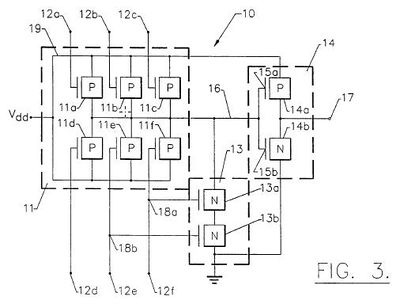

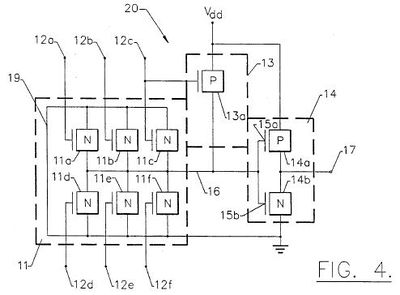

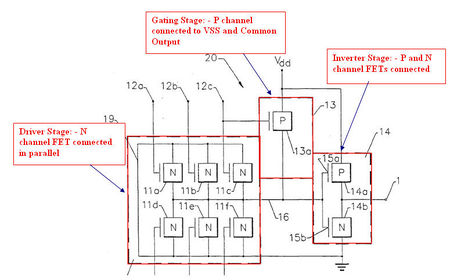

- 开关FET的空间排布: 逻辑门10还包含一开关级13, 所述开关级13包括一对串联在共同输出端16与第二接地端之间的开关晶体管13a和13b。如图3所示,只采用了两个开关晶体管,然而可以采用任意数量的开关晶体管。控制电极18a和18b分别连接到晶体管11f和11e的控制电极12f和12e。相应地,当晶体管11f和11e关闭时开关晶体管13开启。本领域技术人员可以理解,控制电极18可以连接到任何一个控制电极12。

- 相对于驱动级FET的尺寸控制开关FET的尺寸从而形成一个高速逻辑电路。

技术问题二

- 与N沟道器件相比,P沟道器件的饱和电流和载流子迁移率较低,限制了逻辑门的整体速度。

解决方案

- 提供一个高速互补型全并联FET逻辑电路系列,其性能不受P沟道FET器件固有的低饱和电流和低载流子迁移率限制。

- 上述CLIP逻辑电路的速度可通过在P沟道FET器件包含Ge来进一步提高。由于N沟道FET无Ge,所以只有P沟道器件的载流子迁移率会增加。在优选实施例中,Si的P沟道中有38%原子百分比的Ge, 因此P沟道FET和N沟道FET的载流子迁移率基本相同。相应地,P沟道FET的饱和电流限制也降低甚至消除。本领域技术人员可以理解,Ge可以添加到所有互补型FET逻辑电路的P沟道FET中,使得P沟道和N沟道器件的载流子迁移率相当,从而提高了逻辑电路的速度。

技术问题三

- 逻辑门的内部电容也是提高速度的一个主要障碍,栅极的内部电容也会限制一个栅极能够处理的逻辑输入的数量。

解决方案

- 提供一个高速互补型全并联(CLIP)FET逻辑电路系列,其内部电容低,使得一个栅极可以处理大量的逻辑输入。

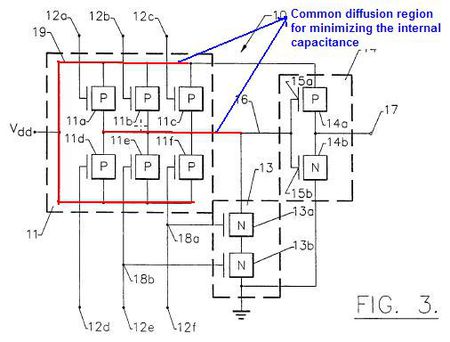

- 互补型全并联逻辑电路的内部电容通过在集成电路中一对驱动级晶体管之间采用共同扩散区来降低。在一对FET驱动晶体管之间采用共同扩散区将共同输出的电容负载降低两倍,从而进一步提高了CLIP逻辑电路的速度。

- 在全并联逻辑电路中采用的共享扩散技术也将扩散电容降低了两倍。

其他电路

钟控CLIP逻辑门

- 在时钟逻辑与门中,当栅极12a-12e和时钟是高电平时,输出17也是高电平。

- 在时钟逻辑或门中,当施加时钟脉冲时,时钟FET21开启和开关FET13关闭。如果任意一个或多个逻辑控制门12a-12f上升,反相器14的输出快速升至电源电位Vdd。当时钟脉冲降到零电位时,时钟FET21关闭和开关FET13开启。此时,共同输出16的电位快速升至电源电位Vdd,和反相器14的输出17快速降到零电位。

闩锁钟控CLIP逻辑与门

- 闩锁钟控CLIP与门——不论输出端12a-12e的电压如何改变,闩锁FET23在时钟周期内确保互补型反相器14的输出17保持不变。

- 闩锁钟控CLIP或门——

- 互补型反相器14的输出17反馈回闩锁FET23a的栅极24a。

- 在时钟脉冲间隔内,如果当其控制端12a-12f处于电源电位时,任何一个驱动级晶体管11a-11e,互补型反相器14的输出17切换到电源电压Vdd。当满足此条件时,FET21和23将互补型反相器输出17闩锁至电源电位,直到时钟脉冲结束。当时钟脉冲电位降到接地电位时,开关FET14开启,时钟FET21关闭,迫使互补型反相器14的输出快速降到接地电位,同时关闭闩锁晶体管23。

专利局的检索报告

- 没有X或Y类对比文件

检索策略

专利检索

- 数据库 - Micropat

| S.No | Scope | Concept | Query | Hits |

| 1 | Claims, Title or Abstract | P or N channel FET’s used to increase the speed, minimize the capacitance, minimize delay time | Query - ((p or n) adj2 (channel or type) NEAR (FET or (field adj1 effect adj1 transistor*))) AND (((increase or step adj1 up or increment or high) NEAR (speed or performance)) OR ((minimize* or reduc* or lower* or (cut adj1 down)) NEAR capacitance) OR ((minimize* or reduc* or lower* or (cut adj1 down)) NEAR delay)) Priority Date (earliest): <19910131 |

134 |

| 2 | Claims, Title or Abstract | Increase the speed of the logic circuits that includes transistors | Query - (increase or step adj1 up or increment or high OR enhanc*) SAME ((logic adj1 (circuit or gate or stage)) AND ((p or n) adj2 (channel or type) NEAR (transistor or *FET*1 or (field adj1 effect adj1 transistor*)))) Priority Date (earliest): <19910131 |

32 |

| 3 | Claims, Title or Abstract | FET’s connected in parallel with the drains connected to Vdd | Query - ((p or n) adj2 (channel or type) NEAR (FET*1 or (field adj1 effect adj1 transistor*))) WITH parallel WITH (Vdd or potential or supply) Priority Date (earliest): <19910131 |

58 |

| 4 | Full patent spec. | FET’s connected in parallel to increase the speed | Query: ((p or n) adj2 (channel or type) NEAR (FET*1 or (field adj1 effect adj1 transistor*))) WITH parallel WITH (Vdd or potential or supply) AND (logic adj1 (circuit or gate)) AND (((increase or step adj1 up or increment or high) NEAR (speed or performance)) OR ((minimize* or reduc* or lower* or (cut adj1 down)) NEAR capacitance) OR ((minimize* or reduc* or lower* or (cut adj1 down)) NEAR delay)) Priority Date (earliest): <19910131 |

33 |

| 5 | Full patent spec. | FET Connection having common output | Query - ((p or n) adj2 (channel or type) NEAR (*FET*1 or (field adj1 effect adj1 transistor*))) SAME (parallel and (Vdd or potential or supply) and (common adj1 output)) Priority Date (earliest): <19910131 |

22 |

| 6 | Full patent spec. | FET’s with channel width, channel lengths and saturation current described | Query: (channel adj1 (width and length)) and (saturation adj1 current) and ((p or n) adj2 (channel or type) NEAR (FET*1 or (field adj1 effect adj1 transistor*))) Priority Date (earliest): <19910131 |

13 |

| 7 | Full patent spec. | FET’s of gating stage connected serially to common output and ground | Query: ((p or n) adj2 (channel or type) NEAR (FET*1 or (field adj1 effect adj1 transistor*))) WITH (((serial or serially) NEAR2 (connected or connection)) and (ground or VSS or potential)) Priority Date (earliest): <19910131 |

98 |

| 8 | Claims | Increasing the speed in the logic circuits | Query - (increase or step adj1 up or increment or high) WITH (logic adj1 (circuit or gate)) AND (transistor or FET*1 or (field effect transisitor*)) and speed Priority Date (earliest): <19910131 |

100 |

| 9 | Full patent spec. | Common diffusion to minimize the internal capacitance | Query: ((common or shared or mutual) WITH diffusion) and ((minimize* or reduc* or lower* or (cut adj1 down)) NEAR capacitance) AND (FET or (field adj1 effect adj1 transistor*) or transistor) Priority Date (earliest): <19910131 | 48 |

| 10 | Full patent spec. | Increasing the carrier mobility in P-channel FET’s by doping germanium | Query - (p adj2 (channel or type) NEAR (transistor or *FET*1 or (field adj1 effect adj1 transistor*))) AND ((increase or step adj1 up or increment or high or enhanc* or equalize) NEAR (carrier NEAR mobilit*)) AND germanium Priority Date (earliest): <19910131 |

12 |

| 11 | Total | 1 OR 2 OR 3 OR 4 OR 5 OR 6 OR 7 OR 8 OR 9 | 542 |

备注: 在其他数据库中采用其算符使用上述检索式进行检索。数据库包括SIP、Google Patent等。

非专利检索

技术文章

- 数据库 - Google scholar that covers IEEE

- 时间范围 - 1985-1990

| S.no | Query | Hits |

| 1 | P N channel FET logic increase OR enhance OR high "speed" | 399 |

| 2 | P channel FET logic speed increase OR enhance OR high "germanium" | 52 |

| 3 | FET logic parallel speed drain increase OR enhance OR high OR Vdd OR potential -patents | 267 |

| 4 | FET logic parallel speed increase OR enhance OR high OR Vdd OR potential "common output" | 30 |

| 5 | P N channel FET logic speed inverter OR complimentary "common output" | 4 |

| 6 | P-channel N-channel FET common diffusion "parallel" | 114 |

| 7 | P-channel N-channel FET germanium increase OR enhance OR high "carrier mobility" | 9 |

| 8 | P-channel N-channel FET germanium increase OR enhance OR high "carrier mobilities" | 3 |

| 9 | P-channel N-channel FET germanium increase OR enhance OR high "saturation current" | 6 |

| 10 | P-channel N-channel FET minimize OR decrease OR reduce "internal capacitance" | 4 |

| 11 | Total | 888 |

期刊文章

- 从BYTE期刊中找到一篇相关文章.

- Gallium Arsenide Chips - Volume 9, issue 12 (November, 1984)

非专利文献分析

分析1

| NAME | CLIP FET | A 15-ns CMOS 64K RAM |

| FIGURE | ||

| TYPE | Patent:- US5247212 | IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SC-21, NO. 5 |

| Title | Complementary logic input parallel (CLIP) logic circuit family | A 15-ns CMOS 64K RAM |

| Assignee | THUNDERBIRD TECH INC (US) | STANLEY E. SCHUSTER, MEMBER, IEEE, BARBARA A. CHAPPELL, MEMBEtt, IEEE, ROBERT L. FRANCH, PAUL F. GREH3R, STEPHEN P. KLEPNER, FANG-SHI J. LA1, MEMBER, IEEE, PETER W. COOK, MEMBER, IEEE, ROBERTA. LIPA, MEMBER, IEEE, REGINALD J. PERRY, WILLIAM F. POKORNY, AND MICHAEL A. ROBERGE |

| IPC | H01L21/8238; H01L27/092; H03K3/356; H03K19/0948; H03K19/096; H01L21/70; H01L27/085; H03K3/00; H03K19/0948; H03K19/096; (IPC1-7): H03K17/04; H03K19/003; H03K19/017; H03K19/094; H03K19/20 | |

| Priority date | 19910131 | |

| Filing date | 19910131 | |

| Publication date | 9/21/1993 | 11/5/1986 |

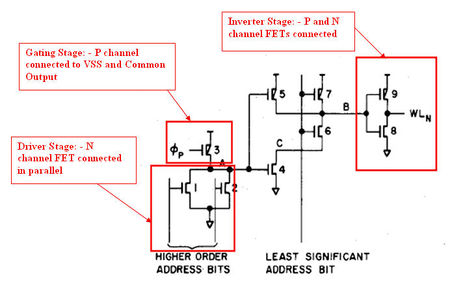

| Driving stage | P channel FET (CLIP AND gate) / N channel FET (CLIP OR gate) | N channel FET |

| Connection 1 | FET being connected between a common output and a first potential level (Vdd) | FET being connected between a common output and GND |

| Connection 2 | Control electrode of driving stage FET for receiving logic input signals (Multiple) | Control electrode of driving stage FET connected to higher order address lines |

| Gating stage | N channel FET (CLIP AND gate) / P channel FET (CLIP OR gate) | P channel FET |

| Connection 1 | FET being connected between a second potential level (Ground or Vss) and common output. | FET being connected between a second potential level Vss and common output. |

| Connection 2 | Control electrode of gating stage FET is connected to a control electrode of driving stage FET, | Control electrode of gating stage FET is directly/indirectly connected to driving stage which is not shown in figure. It is obvious as the working remains same |

| Complementary FET inverter | Complimentary P & N channel FETs | Complimentary P & N channel FETs |

| Connection 1 | FET’s are serially connected between said first and second potential levels (Vdd and (Vss or grnd)) | FET’s are serially connected between said first and second potential levels (Vdd and (Vss or grnd)) |

| Connection 2 | Inverter input being connected to common output. | Inverter input being connected to common output. |

| Zg - channel width of gating transistors, Zd - channel width of driving transistors, I@*satd - saturation current for square channel driving transistor, I@*satg - saturation current for square channel gating transistor, Lg - channel length of gating transistors, Ld - channel length of driving stage transistors, and Sg - number of gating transistors | Since the connections are similar the channel width criteria remains same |

分析 2

- 权利要求21 - Ge掺杂的P沟道FET

- 该对比文件描述了在P沟道FET中掺Ge提高沟道迁移率(第 2630页)

标注文章

结论

- 如上表所示,这篇文章描述了相同的驱动阶段,开关阶段和反相阶段。低阶位增加了另外一个可选的阶段,如未标注阶段的上述表格右边的图中所示。

- 因此,该文章可以将该专利无效掉。

| Contact Dolcera |

|---|

| Email: info@dolcera.com |

| Phone: +1-650-269-7952, +91-40-2355-3493 |